【冒頭説明】

一般社団法人RISC-V協会(所在地:東京都文京区)は、2025年12月4日(木)に東京大学で開催される「RISC-V Day Tokyo 2025 Autumn」において、MIPS Technologiesがプラチナスポンサーとして参画し、登壇発表を行うことを発表しました。本大会は、RISC-V発表15周年を記念し、特別に参加費を無償化して開催され、MIPS TechnologiesがGlobalFoundries統合後、日本初の登壇発表をプラチナスポンサーとして行います。

【発表経緯】

8月19日:「RISC-V誕生15周年記念マグカップ制作・進呈」発表

9月4日:マグカップ デザイン公開

10月24日:協賛企業支援による「無料登録制」への移行発表

11月2日:米国Googleエンジニアによる「デジタル信頼基盤技術」講演発表

11月5日:米国Amazon社によるクラウドとエッジをつなぐ「AIエージェントの未来」についての講演を公表

今回は、MIPS Technologiesがプラチナスポンサーとして登壇発表をすることをお知らせします。

【関連サイト】

開催日:2025年12月4日(木)/会場:東京大学

無料参加登録サイト:https://riscv-day-2025-autumn.peatix.com/view

和文会議情報サイト:https://riscv.or.jp/risc-v-day-tokyo-2025-autumn-public/

英文会議情報サイト:https://riscv.or.jp/en/risc-v-day-tokyo-2025-autumn-public-2/

【今回の登壇の特徴】

■ MIPSとGlobalFoundries統合後の新体制

2025年7月、MIPSは米国の半導体製造大手**GlobalFoundries(GF)によって買収され、同年8月に統合を完了しました。MIPSはGFグループ内で独立した事業ユニット(Independent Business Unit)**として運営されており、米国法管轄下での知的財産の保護と経営上の自律性を維持しています。

一方で、GFの製造プロセス技術とMIPSのRISC-VベースCPU IPを連携させることで、設計と製造のフィードバックを強化する「Design-Foundry協調」体制の構築を進めています。この体制により、設計最適化から量産段階までを一貫して検証できる開発基盤を整備し、AI、自動車、通信、産業機器など幅広い分野でのRISC-Vソリューション提供を加速しています。

■ 日本における初登壇の意義

MIPSがGlobalFoundries統合後の新体制として登壇するのは、今回のRISC-V Day Tokyo 2025 Autumnがアジア初となります。本講演では、RISC-VベースCPU IPの最新ロードマップと、GFとの協調による設計・製造連携の取り組みを紹介する予定です。この発表は、MIPSがオープンISA時代におけるグローバルな再始動を象徴する機会となります。

【RISC-V Day Tokyo 2025 Autumnの特徴】

イベント名: RISC-V Day Tokyo 2025 Autumn

開催日程: 2025年12月4日(木)

会 場: 東京大学 伊藤国際学術研究センター(Ito International Research Center)

住 所: 東京都文京区本郷7丁目3-1

主 催: 一般社団法人RISC-V協会(RISC-V Association Japan)

参加費: 無料(事前登録制)

※本イベントでは、国内外のRISC-V関連企業・研究機関による講演・展示が行われ、MIPSはGlobalFoundries統合後として初の公式登壇を行います。

【本件に関するお問い合わせ】

RISC-V Day Tokyo 2025 Autumn 事務局

E-mail:info@riscv.or.jp

Web:https://riscv.or.jp

電話:03-5565-0565

図1. MIPS Technologiesのロゴ(2025年版)

フォトクレジット:(C) MIPS Technologies/出典: MIPS Technologies公式サイト

出典元:Wikimedia Commons “File:MIPS Logo 2025.svg” - Public Domain / Trademarked Material

一般社団法人RISC-V協会(所在地:東京都文京区)は、2025年12月4日(木)に東京大学で開催される「RISC-V Day Tokyo 2025 Autumn」において、MIPS Technologiesがプラチナスポンサーとして参画し、登壇発表を行うことを発表しました。本大会は、RISC-V発表15周年を記念し、特別に参加費を無償化して開催され、MIPS TechnologiesがGlobalFoundries統合後、日本初の登壇発表をプラチナスポンサーとして行います。

【発表経緯】

8月19日:「RISC-V誕生15周年記念マグカップ制作・進呈」発表

9月4日:マグカップ デザイン公開

10月24日:協賛企業支援による「無料登録制」への移行発表

11月2日:米国Googleエンジニアによる「デジタル信頼基盤技術」講演発表

11月5日:米国Amazon社によるクラウドとエッジをつなぐ「AIエージェントの未来」についての講演を公表

今回は、MIPS Technologiesがプラチナスポンサーとして登壇発表をすることをお知らせします。

【関連サイト】

開催日:2025年12月4日(木)/会場:東京大学

無料参加登録サイト:https://riscv-day-2025-autumn.peatix.com/view

和文会議情報サイト:https://riscv.or.jp/risc-v-day-tokyo-2025-autumn-public/

英文会議情報サイト:https://riscv.or.jp/en/risc-v-day-tokyo-2025-autumn-public-2/

【今回の登壇の特徴】

■ MIPSとGlobalFoundries統合後の新体制

2025年7月、MIPSは米国の半導体製造大手**GlobalFoundries(GF)によって買収され、同年8月に統合を完了しました。MIPSはGFグループ内で独立した事業ユニット(Independent Business Unit)**として運営されており、米国法管轄下での知的財産の保護と経営上の自律性を維持しています。

一方で、GFの製造プロセス技術とMIPSのRISC-VベースCPU IPを連携させることで、設計と製造のフィードバックを強化する「Design-Foundry協調」体制の構築を進めています。この体制により、設計最適化から量産段階までを一貫して検証できる開発基盤を整備し、AI、自動車、通信、産業機器など幅広い分野でのRISC-Vソリューション提供を加速しています。

■ 日本における初登壇の意義

MIPSがGlobalFoundries統合後の新体制として登壇するのは、今回のRISC-V Day Tokyo 2025 Autumnがアジア初となります。本講演では、RISC-VベースCPU IPの最新ロードマップと、GFとの協調による設計・製造連携の取り組みを紹介する予定です。この発表は、MIPSがオープンISA時代におけるグローバルな再始動を象徴する機会となります。

【RISC-V Day Tokyo 2025 Autumnの特徴】

イベント名: RISC-V Day Tokyo 2025 Autumn

開催日程: 2025年12月4日(木)

会 場: 東京大学 伊藤国際学術研究センター(Ito International Research Center)

住 所: 東京都文京区本郷7丁目3-1

主 催: 一般社団法人RISC-V協会(RISC-V Association Japan)

参加費: 無料(事前登録制)

※本イベントでは、国内外のRISC-V関連企業・研究機関による講演・展示が行われ、MIPSはGlobalFoundries統合後として初の公式登壇を行います。

【本件に関するお問い合わせ】

RISC-V Day Tokyo 2025 Autumn 事務局

E-mail:info@riscv.or.jp

Web:https://riscv.or.jp

電話:03-5565-0565

図1. MIPS Technologiesのロゴ(2025年版)

フォトクレジット:(C) MIPS Technologies/出典: MIPS Technologies公式サイト

出典元:Wikimedia Commons “File:MIPS Logo 2025.svg” - Public Domain / Trademarked Material

図2.ソニー初代PlayStation(SCPH-1000型)とコントローラー

1994年に日本で発売された初代モデル。

LSI Logic製**CW33300(MIPS R3000A互換CPU)**を搭載し、

家庭用エンターテインメント機器として初めて本格的なRISCアーキテクチャを採用した。

撮影:Evan Amos(Vanamo Media)/Wikimedia Commons(Public Domain)

図3.任天堂「NINTENDO 64」(1996年発売)

任天堂が1996年に発売した第5世代家庭用ゲーム機。

同世代のセガサターンやソニー・プレイステーションより1年以上遅れて登場したが、

高性能な3Dグラフィックス処理能力を持ち、カートリッジ媒体を採用した。

採用CPUはシリコングラフィックス(SGI)と共同開発したMIPS R4300i(64ビットRISC)。

生涯販売台数は約3,000万台を超え、ソニーのPlayStationに次ぐ販売実績を記録した。

撮影:Evan Amos(Vanamo Media)/Wikimedia Commons(Public Domain)

図4.チップ 「Toshiba TC86R10000-195」

米シリコングラフィックス社のワークステーション向けに東芝が製造した MIPS R10000シリーズの後期版(R12000世代) で、東芝がSGIの委託により製造したチップの写真。

撮影:ZyMOS(CPU Grave Yard)/Wikimedia Commons(CC BY-SA)

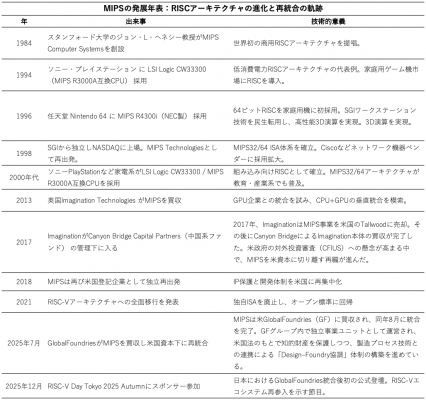

表1.MIPSの発展年表:RISCアーキテクチャの進化と再統合の軌跡